Master's Thesis:

Rhealstone Benchmarking of FreeRTOS and the Xilinx Extensible Processing Platform

Abstract:

|

|

Embedded system designers require deterministic, real-time operating system (RTOS) support for the commonly available processing hardware. The Xilinx Zynq Extensible Processing Platform (EPP) offers software, hardware, and input/output (I/O) programmability on a single chip. The Xilinx Zynq EPP features a Dual ARM Cortex-A9 MPCore, Advanced Microcontroller Bus Architecture (AMBA) Advanced eXtensible Interface 4 (AXI4) interconnect, and Xilinx Kintex-7 series Programmable Logic (PL) which provide the requisite capabilities for the increasing demands of embedded processing applications. The AMBA AXI4 interconnect provides high speed point to point interconnections between the ARM processor cores and the Field Programmable Gate Array (FPGA) structure allowing for rapid data transmission to optimize system performance. The incorporation of an RTOS ensures predictable execution times of applications. Benchmarks, such as the Rhealstone, were developed to provide designers with a method of evaluating and comparing these multitasking RTOSs running on various hardware platforms. This thesis research performs Rhealstone benchmarking and evaluates the AMBA AXI4 interconnect performance while executing FreeRTOS on the ARM core of the Zynq EPP device.

|

|

Thesis Document

The thesis document can be found below.

| timothy_boger_msee_defense.pdf | |

| File Size: | 1115 kb |

| File Type: | |

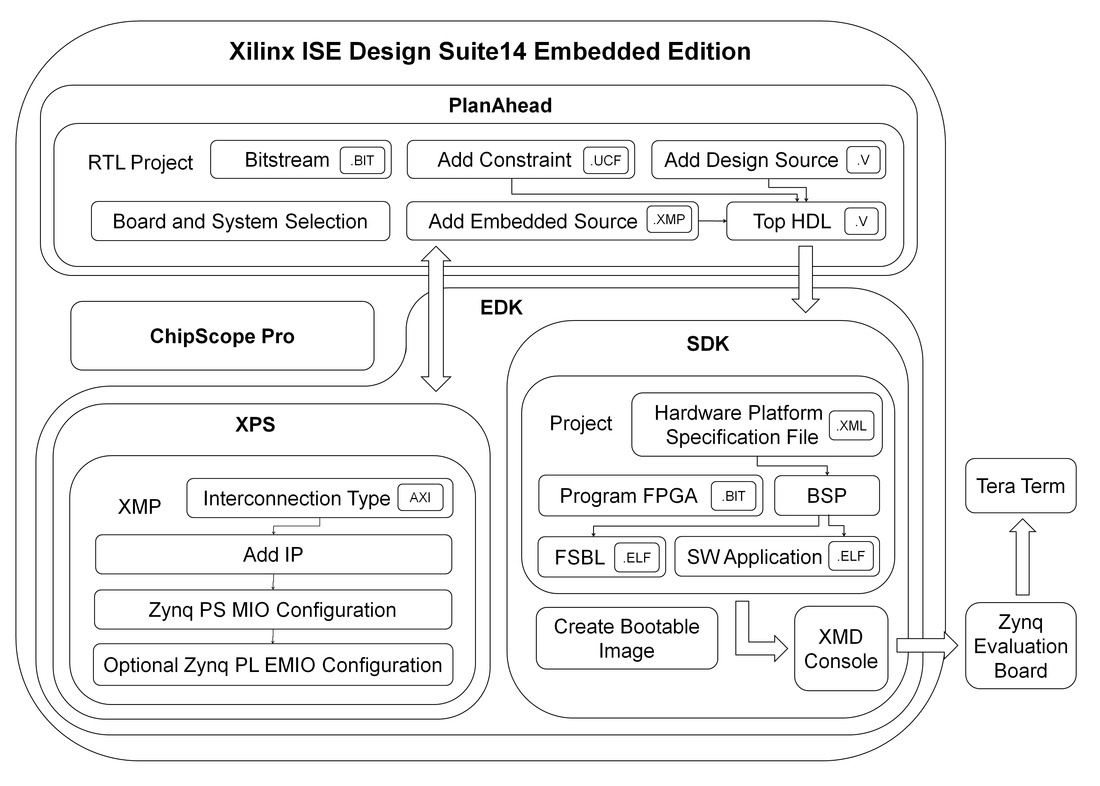

Xilinx ISE Design Suite 14 Embedded Edition Block Diagram

This block diagram was created by me for my thesis. It demonstrates how each of the design tools of the Xilinx ISE Design Suite work together.